This blog is for "Advanced Logic Circuits and Switching Theory" subject. Every documentation and video will be posted here.

Lab 5: 99 Counter

I . Introduction

In digital logic and computing, a counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, often in relationship to a clock signal.

II. Objective

To be able to create a 99 counter with previous code.

IV. Data and result

V. Analysis and Discussion

The 99counter is similar to the previous experiment.We had to produce two number in the two seven segment display and it will count from 0 to 99. Then we have to improve the code to set the value of the 99-Counter.We have some troubles in the display of two digits and the set button.Finally weer able to finish this lab with four functions: Clock, Pause, Reset and Set.

The 99counter is similar to the previous experiment.We had to produce two number in the two seven segment display and it will count from 0 to 99. Then we have to improve the code to set the value of the 99-Counter.We have some troubles in the display of two digits and the set button.Finally weer able to finish this lab with four functions: Clock, Pause, Reset and Set.

VI. Conclusions

By using the last four experiments, the group were able to create a 99-Counter with Clock, Pause, Reset and Set buttons. This was the hardest and longest experiment that we performed. Through this experiment, we have learn more about logic circuit and many more.

By using the last four experiments, the group were able to create a 99-Counter with Clock, Pause, Reset and Set buttons. This was the hardest and longest experiment that we performed. Through this experiment, we have learn more about logic circuit and many more.

Lab 4: Sequential Code

I. Introduction

In digital circuit theory, sequential logic is a type of logic circuit whose output depends not only on the present input but also on the history of the input. This is in contrast to combinational logic, whose output is a function of, and only of, the present input. In other words, sequential logic has state (memory) while combinational logic does not.

In digital circuit theory, sequential logic is a type of logic circuit whose output depends not only on the present input but also on the history of the input. This is in contrast to combinational logic, whose output is a function of, and only of, the present input. In other words, sequential logic has state (memory) while combinational logic does not.

Sequential logic is therefore used to construct some types of computer memory, other types of delay and storage elements, and finite state machines. Most practical computer circuits are a mixture of combinational and sequential logic.

Executed sequentially.

Also called behavioral code.

Part of code that is executed sequentially:

Processes

Functions

Procedures

Variables are also restricted to be used in sequential code only.

II. Objective

To be able to create a sequential logic with sequential code

III.Conceptual Framework

IV. Data and Result

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity segmt_count is

port( set,clk,rst,pause : in std_logic;

I : in std_logic_vector (0 to 3);

segs :buffer std_logic_vector(6 downto 0);

rco : out std_logic);

end segmt_count;

architecture behav of segmt_count is

begin

process(clk, rst, set, pause)

begin

if(rst='0') then segs <= "0000001";

elsif(set ='0') then

case I is

when "0000" => segs <= "0000001";

when "0001" => segs <= "1001111";

when "0010" => segs <= "0010010";

when "0011" => segs <= "0000110";

when "0100" => segs <= "1001100";

when "0101" => segs <= "0100100";

when "0110" => segs <= "0100000";

when "0111" => segs <= "0001111";

when "1000" => segs <= "0000000";

when "1001" => segs <= "0000100";

when others => segs <= "1111111";

end case;

elsif (clk'event and clk ='1') then

if (pause = '0' and (rst='0' or clk='0' or set='0')) then segs <= segs;

elsif(pause = '1') then

case segs is

when "0000001" => segs <= "1001111";

when "1001111" => segs <= "0010010";

when "0010010" => segs <= "0000110";

when "0000110" => segs <= "1001100";

when "1001100" => segs <= "0100100";

when "0100100" => segs <= "0100000";

when "0100000" => segs <= "0001111";

when "0001111" => segs <= "0000000";

when "0000000" => segs <= "0001100";

when others => segs <= "0000001";

end case;

end if;

end if;

end process;

rco <= '1'when (segs = "0000001")else '0';

end behav;

V. Analysis and Discussion

In this experiment, we had four main problems: count, pause, reset and set. The group really got problems with this experiment. Unlike previous experiments, we spent three weeks to find out the errors. Also we got problems with the code and pin assignment. Finally, we were able to finish this experiment.

VI.Conclusion

By using sequential code we were able to create a sequential logic with the Mod -9 counter.By this experiment the group improved the debugging skills and increase the knowledge in programming especially the conditional and case statements.

Lab 3: Concurrent Code

I. Introduction

Concurrent codes are a form of superimposed codes that can be decoded efficiently. It turns out that this property enables the development of a new form of spread spectrum radio communication that offers new ways to address several problems. The key ones that have been identified to date include:

• Unkeyed jam resistance in adversarial environments.

• Jam resistance in public-access networks.

• RFID self-jamming.

• MAC (Media Access Control) protocol simplification in wireless networks.

• Clock recovery and synchronization.

II. Objective

To be able to implement combinational logic circuits with concurrent code and interfaces their symbols with each other.

IV. Data and Result

3.1 3.1 Create a multiplexer for two 4 bits numbers

library IEEE;

use IEEE.std_logic_1164.all;

entity twone is

port (A, B : IN STD_LOGIC_VECTOR(3 downto 0);

S : IN BIT;

X : OUT STD_LOGIC_VECTOR(3 downto 0));

end twone;

architecture fourbit of twone is

begin

process (S)

begin

if (S = '0') then

X<=A;

else

X<=B;

end if;

end process;

end fourbit;

3.2 Design a Comparator for two 4 bits numbers using VHDL. If A>B, the output is 1.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

entity twofour is

port (x, y : IN BIT_VECTOR (3 downto 0);

z : OUT BIT);

end twofour;

architecture behavior of twofour is

begin

z<= '1' when (x>y) else '0';

end behavior;

library IEEE;

use IEEE.std_logic_1164.all;

entity twone is

port (A, B : IN STD_LOGIC_VECTOR(3 downto 0);

S : IN BIT;

X : OUT STD_LOGIC_VECTOR(3 downto 0));

end twone;

architecture fourbit of twone is

begin

process (S)

begin

if (S = '0') then

X<=A;

else

X<=B;

end if;

end process;

end fourbit;

3.2 Design a Comparator for two 4 bits numbers using VHDL. If A>B, the output is 1.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

entity twofour is

port (x, y : IN BIT_VECTOR (3 downto 0);

z : OUT BIT);

end twofour;

architecture behavior of twofour is

begin

z<= '1' when (x>y) else '0';

end behavior;

Lab 2: VDHL Familiarization

I. Introduction

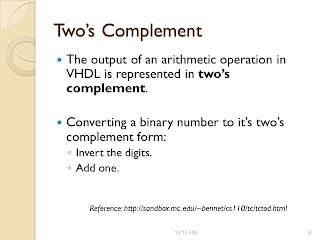

VHSIC (Very High Speed Integrated Circuits) Hardware Description Language

Used to describe the behavior of an electronic circuit or system

Two applications of VHDL

Programmable Logic Devices

Application Specific Integrated Circuits.

Click here for more information.

II. Objective

To be able to implement logic circuit design in VHDL code.

III. Conceptual framework

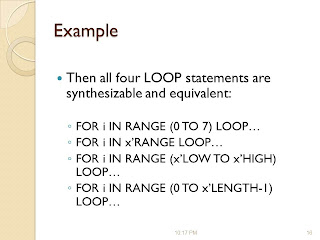

1. Concurrent Execution

VHDL statements are inherently concurrent (parallel)

For this reason, VHDL is usually referred to as a code rather than a program.

Only statements inside a PROCESS, FUNCTION, or PROCEDURE are executed sequentially.

2. Advantages of Using VHDL

Allows the behaviour of the required system to be described (modelled) and verified (simulated) before synthesis tools translate the design into real hardware (gates and wires).

Allows the description of a concurrent system (many parts, each with its own sub-behaviour, working together at the same time).

Supports in-system programmability.

◦ Program and reprogram devices after they are soldered onto the printed circuit board (PCB), minimizing the possibility of lead damage or electrostatic discharge (ESD) exposure.

Upgrade systems in the field after they have been shipped.

III. Data and Result

1. Experiment 2A

Data

library IEEE;

use IEEE.std_logic_1164.all;

entity DEC is

port( A, B, C, D : in bit;

E, F, G, H, I, J, K : out bit );

end DEC;

architecture DEC1 of DEC is

begin

E <= NOT((NOT A AND B AND D) OR

(A AND NOT B AND NOT C) OR

(NOT B AND NOT D) OR

(NOT A AND C) OR

(B AND C));

F <= NOT((NOT A AND NOT C AND NOT D) OR

(NOT A AND C AND D) OR

(A AND NOT C AND D) OR

(NOT B AND NOT C) OR

(NOT B AND NOT D));

G <= NOT((NOT B AND NOT C) OR

(NOT B AND D) OR

(NOT C AND D) OR

(NOT A AND B) OR

(A AND NOT B));

H <= NOT((NOT B AND NOT C AND NOT D) OR

(NOT B AND C AND D) OR

(NOT A AND C AND NOT D) OR

(B AND NOT C AND D) OR

(A AND B AND NOT D) OR

(A AND NOT C));

I <= NOT((NOT B AND NOT D) OR

(C AND NOT D) OR

(A AND B) OR

(A AND C));

J <= NOT((NOT B AND NOT C AND NOT D) OR

(NOT A AND B AND NOT C) OR

(B AND C AND NOT D) OR

(A AND C) OR

(A AND NOT B));

K <= NOT((NOT B AND C) OR

(B AND NOT C) OR

(B AND NOT D) OR A);

end DEC1;

Result:

2. Experiment 2B

Data

library IEEE;

use IEEE.std_logic_1164.all;

entity MUX is

port( s0, s1, s2, a, b, c, d, e, f, g, h : in bit;

y : out bit );

end MUX;

architecture MUX1 of MUX is

begin

y <= (a AND NOT s0 AND NOT s1 AND NOT s2) OR

(b AND NOT s0 AND NOT s1 AND s2) OR

(c AND NOT s0 AND s1 AND NOT s2) OR

(d AND NOT s0 AND s1 AND s2) OR

(e AND s0 AND NOT s1 AND NOT s2) OR

(f AND s0 AND NOT s1 AND s2) OR

(g AND s0 AND s1 AND NOT s2) OR

(h AND s0 AND s1 AND s2);

end MUX1;

Result

V. Analysis

In this experiment 2, programming defines the whole circuit design. First we have made some errors in the program because we are not familiar with the other functions of Quartus II. Apparently we have the notes in the powerpoint presentation and use the functions that is specified in the slides. So this experiment was easy because we need to know the different functions of the Quartus II and we have to analyze and understand the problem very well.

VI. Conclusion

In this experiment, our group were able to create a logic circuit using VHDL. We were able to use Quartus II version 11 software to create the VHDL. The experiment was easy for us and it focused on the programming. But we cannot avoid those errors except for the warning part. In this software it can directly show the errors in our program.

In this experiment, our group were able to create a logic circuit using VHDL. We were able to use Quartus II version 11 software to create the VHDL. The experiment was easy for us and it focused on the programming. But we cannot avoid those errors except for the warning part. In this software it can directly show the errors in our program.

Lab 1: Quartus II Familiarization

I. Introduction

- An implementation of VHDL and Verilog for hardware description.

- Visual edition of logic circuits.

- Vector waveform simulation.

Quartus II is a software tool produced by Altera for analysis and synthesis of VHDL designs, which enables the developer to compile their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer.

For more information, you may visit this site

II. Objective

To be able to create circuit design in Quartus II.

III.Conceptual Framework

1.Decoder

A decoder is a device which does the reverse of an encoder, undoing the encoding so that the original information can be retrieved. The same method used to encode is usually just reversed in order to decode. It is a combinational circuit that converts binary information from n input lines to a maximum of 2n unique output lines.

In digital electronics, a decoder can take the form of a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different. e.g. n-to-2n, binary-coded decimal decoders. Enable inputs must be on for the decoder to function, otherwise its outputs assume a single "disabled" output code word. Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding.

The example decoder circuit would be an AND gate because the output of an AND gate is "High" (1) only when all its inputs are "High." Such output is called as "active High output". If instead of AND gate, the NAND gate is connected the output will be "Low" (0) only when all its inputs are "High". Such output is called as "active low output".

2. Multiplexer

An electronics, a multiplexer (or mux) is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. A multiplexer of 2n inputs has n select lines, which are used to select which input line to send to the output. Multiplexers are mainly used to increase the amount of data that can be sent over the network within a certain amount of time and bandwidth. A multiplexer is also called a data selector.

An electronic multiplexer makes it possible for several signals to share one device or resource, for example one A/D converter or one communication line, instead of having one device per input signal.

On the other hand, a demultiplexer (or demux) is a device taking a single input signal and selecting one of many data-output-lines, which is connected to the single input. A multiplexer is often used with a complementary demultiplexer on the receiving end.

An electronic multiplexer can be considered as a multiple-input, single-output switch, and a demultiplexer as a single-input, multiple-output switch. The schematic symbol for a multiplexer is an isosceles trapezoid with the longer parallel side containing the input pins and the short parallel side containing the output pin. The schematic on the right shows a 2-to-1 multiplexer on the left and an equivalent switch on the right. The sel wire connects the desired input to the output.

IV.Data and result

V. Analysis

Quartus II is a very useful and easy to use program. Since this was our first experiment, that's why we experienced different errors like the wrong assigning of pins and the wrong connection of wires to the right input of the Integrated Circuit.

VI. Conclusion

By using Quartus II, we were able to create logic circuits with decoder and multiplexer. Since we have took the Logic circuit last semester so we did not have any problem with the gates but there was some problems with the pins assignment . Hopefully we can improve our skill in next lab.

Đăng ký:

Nhận xét (Atom)